# MSP50C614 Mixed-Signal Processor User's Guide

SPSU014 January 2000

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

## Preface

## **Read This First**

## About This Manual

This user's guide gives information for the MSP50C61 mixed-signal processor. This information includes a functional overview, a detailed architectural description, device peripheral functional description, assembly language instruction listing, code development tools, applications, customer information, and electrical characteristics (in data sheet). This document also contains information for the MSP50C604 and MSP50C605, which are in the Product Preview stage of development.

### How to Use This Manual

This document contains the following chapters:

- Chapter 1 Introduction to the MSP50C614

- Chapter 2 MSP50C614 Architecture

- Chapter 3 Peripheral Functions

- Chapter 4 Assembly Language Instructions

- Chapter 5 Code Development Tools

- Chapter 6 Applications

- Chapter 7 Customer Information

- Appendix A MSP50C605 Preliminary Data

- Appendix B MSP50C604 Preliminary Data

- Appendix C MSP50C605 Data Sheet

### Notational Conventions

This document uses the following conventions.

Program listings, program examples, and interactive displays are shown in a special typeface similar to a typewriter's. Examples use a bold **version** of the special typeface for emphasis; interactive displays use a **bold version** of the special typeface to distinguish commands that you enter from items that the system displays (such as prompts, command output, error messages, etc.).

Here is a sample program listing:

| 0011 | 0005 | 0001 | .field | 1, | 2 |

|------|------|------|--------|----|---|

| 0012 | 0005 | 0003 | .field | 3, | 4 |

| 0013 | 0005 | 0006 | .field | б, | 3 |

| 0014 | 0006 |      | .even  |    |   |

Here is an example of a system prompt and a command that you might enter:

C: csr -a /user/ti/simuboard/utilities

In syntax descriptions, the instruction, command, or directive is in a **bold** typeface font and parameters are in an *italic typeface*. Portions of a syntax that are in **bold** should be entered as shown; portions of a syntax that are in *italics* describe the type of information that should be entered. Here is an example of a directive syntax:

.asect "section name", address

.asect is the directive. This directive has two parameters, indicated by *section name* and *address*. When you use .asect, the first parameter must be an actual section name, enclosed in double quotes; the second parameter must be an address.

Square brackets ([ and ] ) identify an optional parameter. If you use an optional parameter, you specify the information within the brackets; you don't enter the brackets themselves. Here's an example of an instruction that has an optional parameter:

LALK 16–bit constant [, shift]

The LALK instruction has two parameters. The first parameter, *16-bit constant*, is required. The second parameter, *shift*, is optional. As this syntax shows, if you use the optional second parameter, you must precede it with a comma.

Square brackets are also used as part of the pathname specification for VMS pathnames; in this case, the brackets are actually part of the pathname (they are not optional).

Braces ( { and } ) indicate a list. The symbol | (read as or) separates items within the list. Here's an example of a list:

{ \* | \*+ | \*- }

This provides three choices: \*, \*+, or \*-.

Unless the list is enclosed in square brackets, you must choose one item from the list.

Some directives can have a varying number of parameters. For example, the .byte directive can have up to 100 parameters. The syntax for this directive is:

.byte value<sub>1</sub> [, ... , value<sub>n</sub>]

This syntax shows that .byte must have at least one value parameter, but you have the option of supplying additional value parameters, separated by commas.

### Information About Cautions and Warnings

This book may contain cautions and warnings.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

This is an example of a warning statement.

A warning statement describes a situation that could potentially cause harm to <u>you</u>.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

## Trademarks

Intel, i486, and Pentium are trademarks of Intel Corporation.

Microsoft, Windows, Windows 95, and Windows 98 are registered trademarks of Microsoft Corporation.

# Contents

| 1 | Introd |          | to the MSP50C614                       |      |

|---|--------|----------|----------------------------------------|------|

|   | 1.1    |          | es of the C614                         |      |

|   | 1.2    |          | ations                                 |      |

|   | 1.3    |          | pment Device: MSP50P614                |      |

|   | 1.4    |          | onal Description                       |      |

|   | 1.5    |          | and C604 (Preliminary Information)     |      |

|   | 1.6    | Termina  | al Assignments and Signal Descriptions | 1-10 |

| 2 | MSP5   | 0C614    | Architecture                           | 2-1  |

|   | 2.1    | Archite  | cture Overview                         | 2-2  |

|   | 2.2    | Compu    | Itation Unit                           | 2-5  |

|   |        | 2.2.1    | Multiplier                             | 2-5  |

|   |        | 2.2.2    | Arithmetic Logic Unit                  | 2-7  |

|   | 2.3    |          | lemory Address Unit                    | 2-11 |

|   |        | 2.3.1    | RAM Configuration                      |      |

|   |        | 2.3.2    | Data Memory Addressing Modes           |      |

|   | 2.4    | 0        | m Counter Unit                         |      |

|   | 2.5    | •        | ic Unit                                |      |

|   | 2.6    |          | y Organization: RAM and ROM            |      |

|   |        | 2.6.1    | Memory Map                             |      |

|   |        | 2.6.2    | Peripheral Communications (Ports)      |      |

|   |        | 2.6.3    | Interrupt Vectors                      |      |

|   |        | 2.6.4    | ROM Code Security                      |      |

|   |        | 2.6.5    | Macro Call Vectors                     |      |

|   | 2.7    |          | pt Logic                               |      |

|   | 2.8    |          | Registers                              |      |

|   | 2.9    |          | Control                                |      |

|   |        | 2.9.1    | Oscillator Options                     |      |

|   |        | 2.9.2    | PLL Performance                        |      |

|   |        | 2.9.3    | Clock Speed Control Register           |      |

|   |        | 2.9.4    | RTO Oscillator Trim Adjustment         |      |

|   | 2.10   |          | ion Timing                             |      |

|   | 2.11   | Reduce   | ed Power Modes                         | 2-34 |

| 3 | Perip  | heral Fu | unctions                               | 3-1  |

|   | 3.1    | I/O      |                                        | 3-2  |

|   |      | 3.1.1    | General-Purpose I/O Ports                                   | 3-2    |

|---|------|----------|-------------------------------------------------------------|--------|

|   |      | 3.1.2    | Dedicated Input Port F                                      | 3-4    |

|   |      | 3.1.3    | Dedicated Output Port G                                     | 3-5    |

|   |      | 3.1.4    | Branch on D Port                                            |        |

|   |      | 3.1.5    | Internal and External Interrupts                            | 3-6    |

|   | 3.2  | Digital- | to-Analog Converter (DAC)                                   | 3-8    |

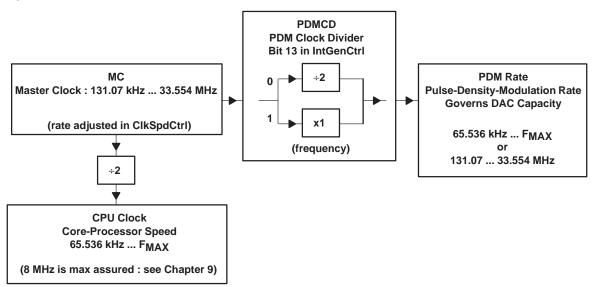

|   |      | 3.2.1    | Pulse-Density Modulation Rate                               | 3-8    |

|   |      | 3.2.2    | DAC Control and Data Registers                              |        |

|   |      | 3.2.3    | PDM Clock Divider                                           | . 3-10 |

|   | 3.3  | Compa    | rator                                                       | . 3-14 |

|   | 3.4  | Interrup | ot/General Control Register                                 | . 3-17 |

|   | 3.5  | Hardwa   | are Initialization States                                   | . 3-19 |

| 4 | Asse | mbly La  | nguage Instructions                                         | 4-1    |

|   | 4.1  | Introdu  | ction                                                       | 4-2    |

|   | 4.2  | System   | n Registers                                                 | 4-2    |

|   |      | 4.2.1    | Multiplier Register (MR)                                    | 4-2    |

|   |      | 4.2.2    | Shift Value Register (SV)                                   | 4-2    |

|   |      | 4.2.3    | Data Pointer Register (DP)                                  |        |

|   |      | 4.2.4    | Program Counter (PC)                                        |        |

|   |      | 4.2.5    | Top of Stack, (TOS)                                         |        |

|   |      | 4.2.6    | Product High Register (PH)                                  |        |

|   |      | 4.2.7    | Product Low Register (PL)                                   |        |

|   |      | 4.2.8    | Accumulators (AC0–AC31)                                     |        |

|   |      | 4.2.9    | Accumulator Pointers (AP0–AP3)                              | 4-5    |

|   |      | 4.2.10   | Indirect Register (R0–R7)                                   | 4-5    |

|   |      | 4.2.11   | String Register (STR)                                       | 4-6    |

|   |      | 4.2.12   | Status Register (STAT)                                      | 4-6    |

|   | 4.3  | Instruct | tion Syntax and Addressing Modes                            | 4-8    |

|   |      | 4.3.1    | MSP50P614/MSP50C614 Instruction Syntax                      | 4-8    |

|   |      | 4.3.2    | Addressing Modes                                            | 4-9    |

|   |      | 4.3.3    | Immediate Addressing                                        | . 4-13 |

|   |      | 4.3.4    | Direct Addressing                                           | . 4-14 |

|   |      | 4.3.5    | Indirect Addressing                                         | . 4-15 |

|   |      | 4.3.6    | Relative Addressing                                         | . 4-16 |

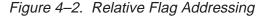

|   |      | 4.3.7    | Flag Addressing                                             | . 4-19 |

|   |      | 4.3.8    | Tag/Flag Bits                                               | . 4-20 |

|   | 4.4  | Instruct | tion Classification                                         | . 4-22 |

|   |      | 4.4.2    | Class 2 Instructions: Accumulator and Constant Reference    | . 4-28 |

|   |      | 4.4.3    | Class 3 Instruction: Accumulator Reference                  | . 4-30 |

|   |      | 4.4.4    | Class 4 Instructions: Address Register and Memory Reference | . 4-34 |

|   |      | 4.4.5    | Class 5 Instructions: Memory Reference                      | . 4-36 |

|   |      | 4.4.6    | Class 6 Instructions: Port and Memory Reference             |        |

|   |      | 4.4.7    | Class 7 Instructions: Program Control                       |        |

|   |      |          |                                                             |        |

|   |      | 4.4.8   | Class 8 Instructions: Logic and Bit                | 4-41  |

|---|------|---------|----------------------------------------------------|-------|

|   |      | 4.4.9   | Class 9 Instructions: Miscellaneous                | 4-42  |

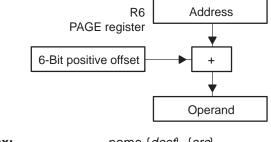

|   | 4.5  | Bit, By | te, Word and String Addressing                     | 4-44  |

|   | 4.6  | MSP50   | P614/MSP50C614 Computational Modes                 | 4-49  |

|   | 4.7  | Hardwa  | are Loop Instructions                              | 4-53  |

|   | 4.8  | String  | Instructions                                       | 4-55  |

|   | 4.9  | Lookup  | Instructions                                       | 4-57  |

|   | 4.10 | Input/C | Dutput Instructions                                | 4-59  |

|   | 4.11 | Specia  | I Filter Instructions                              | 4-59  |

|   | 4.12 |         | ionals                                             |       |

|   | 4.13 |         |                                                    |       |

|   | 4.14 |         | ual Instruction Descriptions                       |       |

|   | 4.15 |         | tion Set Encoding                                  |       |

|   | 4.16 | Instruc | tion Set Summary                                   | 4-196 |

| 5 | Code | Develo  | pment Tools                                        | 5-1   |

| - | 5.1  |         | rction                                             |       |

|   | 5.2  | MSP50   | C6xx Software Development Tool                     | 5-3   |

|   | 5.3  |         | ements                                             |       |

|   | 5.4  | •       | are Installation                                   |       |

|   | 5.5  | Softwa  | re Installation                                    | 5-6   |

|   | 5.6  | Softwa  | re Emulator                                        | 5-13  |

|   |      | 5.6.1   | The Open Screen                                    | 5-13  |

|   |      | 5.6.2   | Projects                                           | 5-15  |

|   |      | 5.6.3   | Description of Windows                             | 5-16  |

|   |      | 5.6.4   | Debugging a Program                                | 5-22  |

|   |      | 5.6.5   | Initializing Chip                                  | 5-27  |

|   |      | 5.6.6   | Emulator Options                                   | 5-28  |

|   |      | 5.6.7   | Emulator Online Help System                        | 5-30  |

|   |      | 5.6.8   | Known Differences, Incompatibilities, Restrictions | 5-32  |

|   | 5.7  | Assem   | bler                                               | 5-33  |

|   |      | 5.7.1   | Assembler DLL                                      | 5-33  |

|   |      | 5.7.2   | Assembler Directives                               | 5-34  |

|   | 5.8  | Linker  |                                                    | 5-38  |

|   | 5.9  |         | ompiler                                            |       |

|   |      | 5.9.1   | Foreword                                           | 5-40  |

|   |      | 5.9.2   | Variable Types                                     |       |

|   |      | 5.9.3   | External References                                | 5-41  |

|   |      | 5.9.4   | CDirectives                                        | 5-42  |

|   |      | 5.9.5   | Include Files                                      |       |

|   |      | 5.9.6   | Function Prototypes and Declarations               |       |

|   |      | 5.9.7   | Initializations                                    |       |

|   |      | 5.9.8   | RAM Usage                                          |       |

|   |      | 5.9.9   | Variable Types                                     | 5-45  |

Contents

ix

|   | 5.10       | <ul> <li>5.9.10 String Functions .</li> <li>5.9.11 Constant Functions .</li> <li>Implementation Details .</li> <li>5.10.1 Comparisons .</li> <li>5.10.2 Division .</li> <li>5.10.3 Function Calls .</li> <li>5.10.4 Programming Example .</li> <li>5.10.5 Programming Example, C – With Assembly Routines .</li> </ul> | 5-47<br>5-48<br>5-48<br>5-50<br>5-50<br>5-51 |

|---|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 5.11       | Beware of Stack Corruption                                                                                                                                                                                                                                                                                             |                                              |

|   | 5.12       | Reported Bugs With Code Development Tool                                                                                                                                                                                                                                                                               |                                              |

| 6 | Appli      | ications                                                                                                                                                                                                                                                                                                               | 6-1                                          |

|   | 6.1        | Application Circuits                                                                                                                                                                                                                                                                                                   |                                              |

|   | 6.2        | MSP50C614/MSP50P614 Initialization Codes                                                                                                                                                                                                                                                                               | 6-4                                          |

|   |            | 6.2.1 File init.asm                                                                                                                                                                                                                                                                                                    |                                              |

|   | 6.3        | Texas Instruments C614 Synthesis Code                                                                                                                                                                                                                                                                                  |                                              |

|   | ~ /        | 6.3.1 Memory Overlay                                                                                                                                                                                                                                                                                                   |                                              |

|   | 6.4        | ROM Usage With Respect to Various Synthesis Algorithms                                                                                                                                                                                                                                                                 | 6-14                                         |

| 7 | Cust       | omer Information                                                                                                                                                                                                                                                                                                       |                                              |

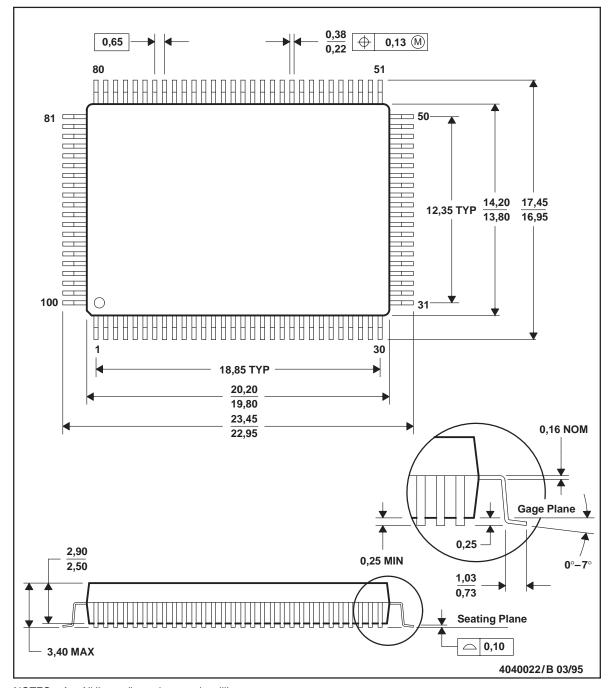

|   | 7.1        | Mechanical Information                                                                                                                                                                                                                                                                                                 |                                              |

|   |            | 7.1.1 Die Bond-Out Coordinates                                                                                                                                                                                                                                                                                         |                                              |

|   |            | 7.1.2 Package Information                                                                                                                                                                                                                                                                                              |                                              |

|   | 7.2<br>7.3 | Customer Information Fields in the ROM                                                                                                                                                                                                                                                                                 |                                              |

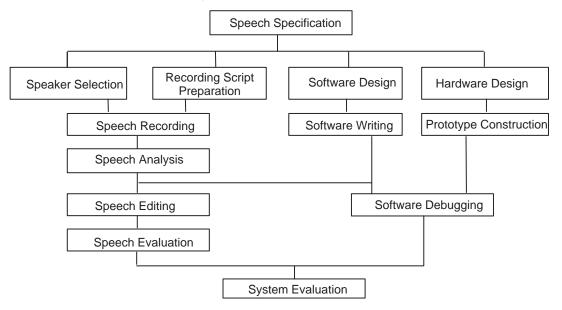

|   | 7.3<br>7.4 | Speech Development Cycle         Device Production Sequence                                                                                                                                                                                                                                                            |                                              |

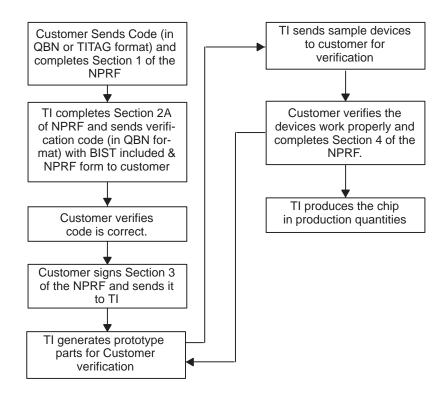

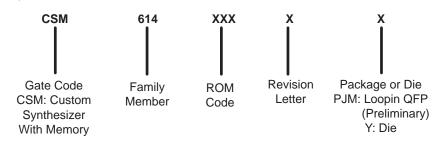

|   | 7.5        | Ordering Information                                                                                                                                                                                                                                                                                                   |                                              |

|   | 7.6        | New Product Release Forms                                                                                                                                                                                                                                                                                              |                                              |

|   |            |                                                                                                                                                                                                                                                                                                                        |                                              |

| Α | A.1        | 50C605 Preliminary Data                                                                                                                                                                                                                                                                                                |                                              |

|   | A.1<br>A.2 | Features                                                                                                                                                                                                                                                                                                               |                                              |

|   | A.3        | Architecture                                                                                                                                                                                                                                                                                                           |                                              |

|   | 7.10       | A.3.1 RAM                                                                                                                                                                                                                                                                                                              |                                              |

|   |            | A.3.2 ROM                                                                                                                                                                                                                                                                                                              |                                              |

|   |            | A.3.3 I/O Pins                                                                                                                                                                                                                                                                                                         | A-3                                          |

| в | MSP!       | 50C604 Preliminary Data                                                                                                                                                                                                                                                                                                | B-1                                          |

| _ | B.1        |                                                                                                                                                                                                                                                                                                                        |                                              |

|   | B.2        | Features                                                                                                                                                                                                                                                                                                               |                                              |

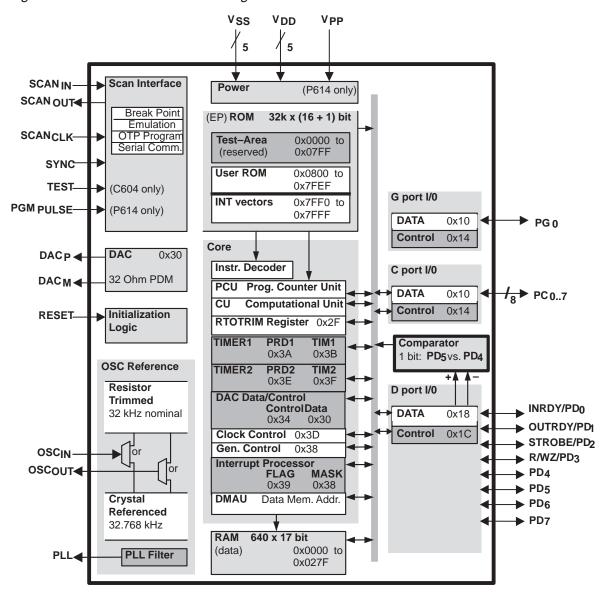

|   | B.3        | Architecture                                                                                                                                                                                                                                                                                                           | B-2                                          |

|   |            | B.3.1 RAM                                                                                                                                                                                                                                                                                                              |                                              |

|   |            | B.3.2 ROM                                                                                                                                                                                                                                                                                                              |                                              |

|   |            | B.3.3 I/O Pins                                                                                                                                                                                                                                                                                                         |                                              |

|   |            | B.3.4 Slave Mode Operation                                                                                                                                                                                                                                                                                             | B-5                                          |

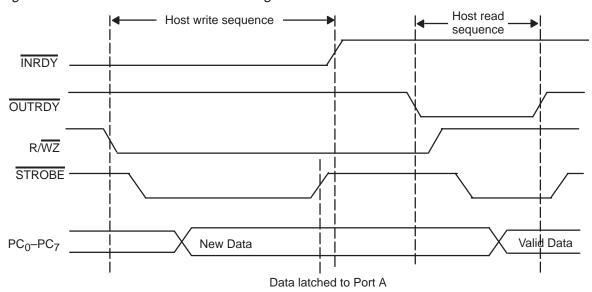

|   | D 4  | B.3.6<br>B.3.7 | Host Write S<br>Host Read S<br>Interrupts   | equence | <br> | <br> | <br> | <br> | B-5<br>B-7 |

|---|------|----------------|---------------------------------------------|---------|------|------|------|------|------------|

| С | MSP5 | 0C605          | ing<br><b>Data Sheet .</b><br>IC605 Data Si |         | <br> | <br> | <br> | <br> | C-1        |

# Figures

| 1–1<br>1–2<br>1–3<br>1–4<br>1–5                                     | Functional Block Diagram for the C614       1-7         Oscillator and PLL Connection       1-8         RESET Circuit       1-9         MSP50C614 100 Pin PJM PLastic Package Pinout       1-12         120 Pin Grid Array Package for the Development Device, P614       1-13                                                                                             |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

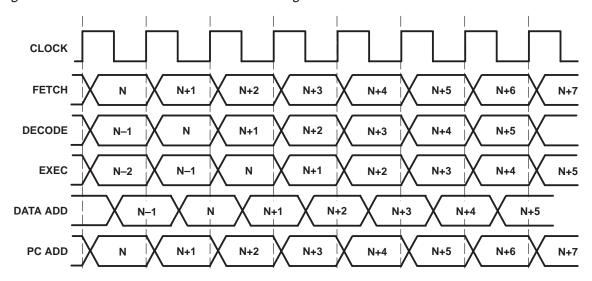

| 2–1<br>2–2<br>2–3<br>2–4<br>2–5<br>2–6<br>2–7<br>2–8<br>2–9<br>2–10 | MSP50C614 Core Processor Block Diagram2-3Computational Unit Block Diagram2-4Overview of the Multiplier Unit Operation2-7Overview of the Arithmetic Logic Unit2-9Overview of the Arithmetic Logic Unit2-10Data Memory Address Unit2-12C614 Memory Map (not drawn to scale)2-16Interrupt Initialization Sequence2-25PLL Performance2-30Instruction Execution and Timing2-34  |

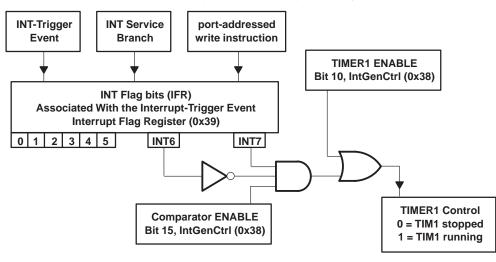

| 3–1<br>3–2                                                          | PDM Clock Divider       3-10         Relationship Between Comparator/Interrupt Activity and the TIMER1 Control       3-15                                                                                                                                                                                                                                                  |

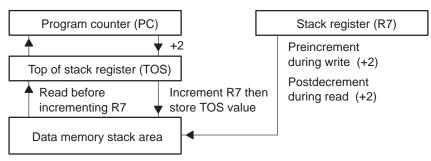

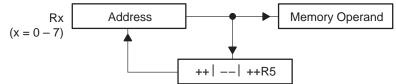

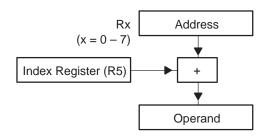

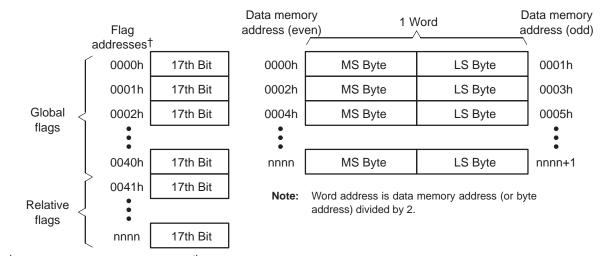

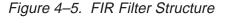

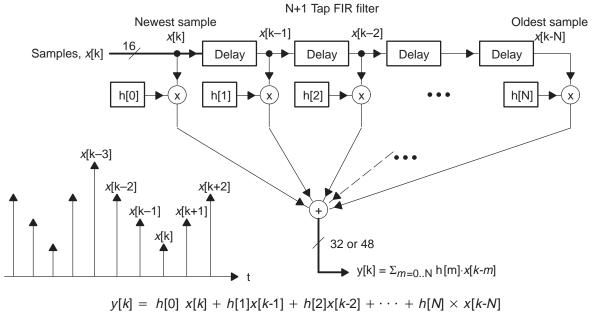

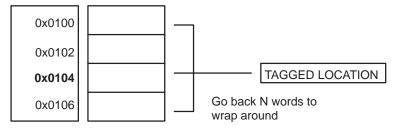

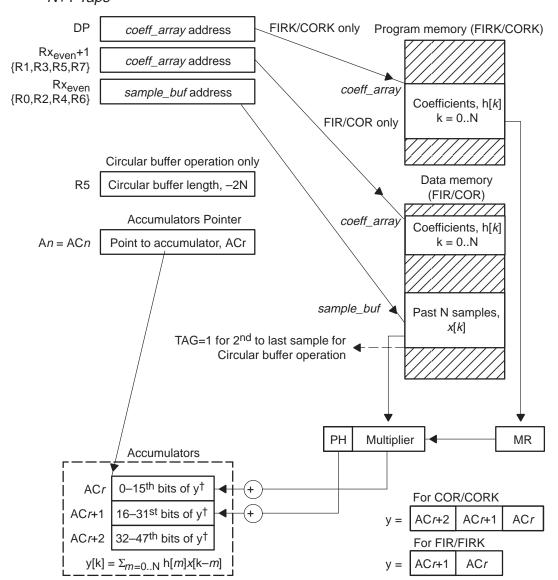

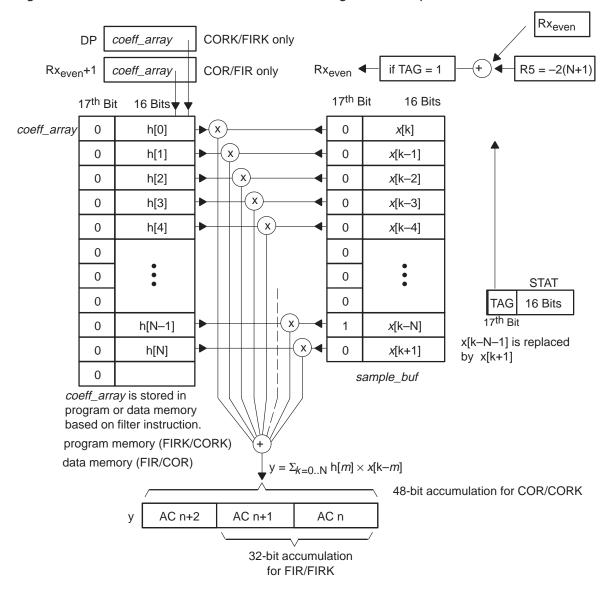

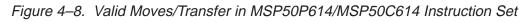

| 4–1<br>4–2<br>4–3<br>4–4<br>4–5<br>4–6<br>4–7<br>4–8                | Top of Stack (TOS) Register Operation4-3Relative Flag Addressing4-19Data Memory Organization and Addressing4-45Data Memory Example4-47FIR Filter Structure4-59Setup and Execution of MSP50P614/MSP50C614 Filter Instructions, N+1 Taps4-67Filter Instruction and Circular Buffering for N+1 Tap Filter4-68Valid Moves/Transfer in MSP50P614/MSP50C614 Instruction Set4-131 |

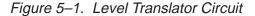

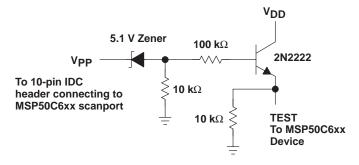

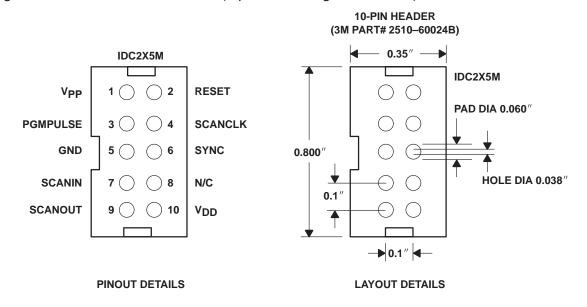

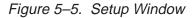

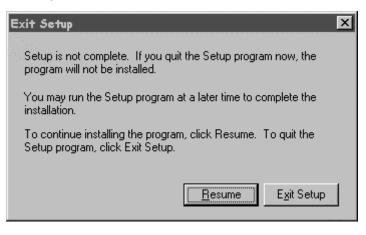

| 5–1<br>5–2<br>5–3<br>5–4<br>5–5<br>5–6<br>5–7<br>5–8                | Level Translator Circuit5-3Hardware Installation5-510-Pin IDC Connector5-6InstallShield Window5-6Setup Window5-7Exit Setup Dialog5-8User Information Dialog5-8Choose Destination Location Dialog5-9                                                                                                                                                                        |

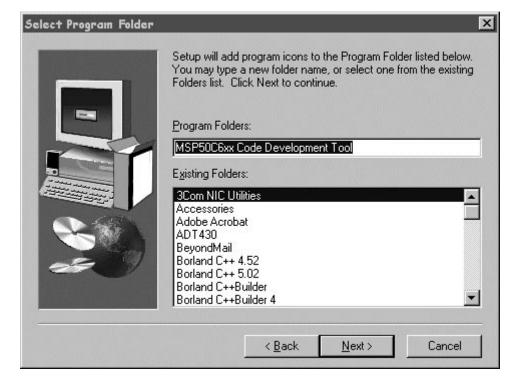

| 5–9  | Select Program Folder Dialog 5-10                           |

|------|-------------------------------------------------------------|

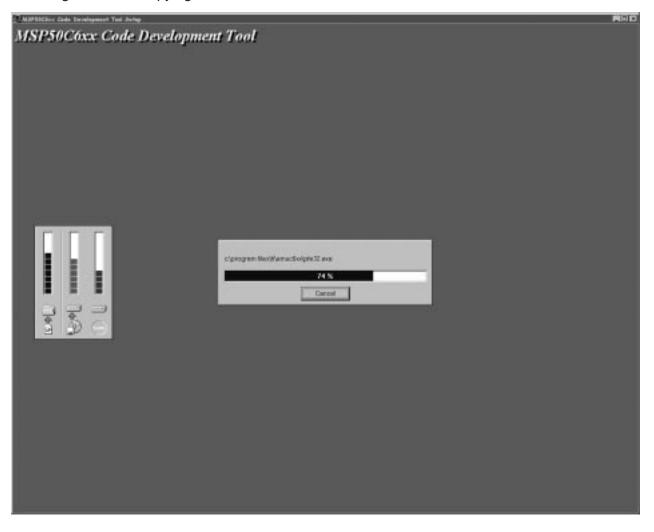

| 5–10 | Copying Files                                               |

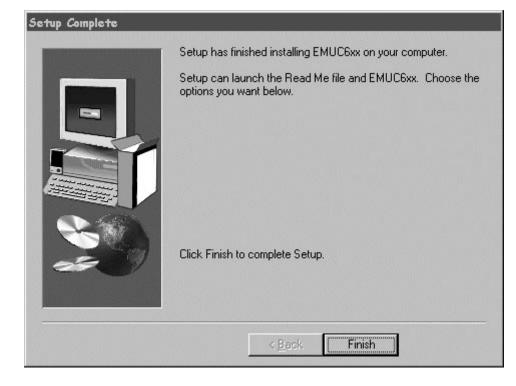

| 5–11 | Setup Complete Dialog 5-12                                  |

| 5–12 | Open Screen                                                 |

| 5–13 | Project Menu 5-14                                           |

| 5–14 | Project Open Dialog 5-14                                    |

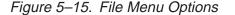

| 5–15 | File Menu Options 5-15                                      |

| 5–16 | MSP50P614/MSP50C614 Code Development Windows                |

| 5–17 | RAM Window                                                  |

| 5–18 | CPU Window                                                  |

| 5–19 | Program Window                                              |

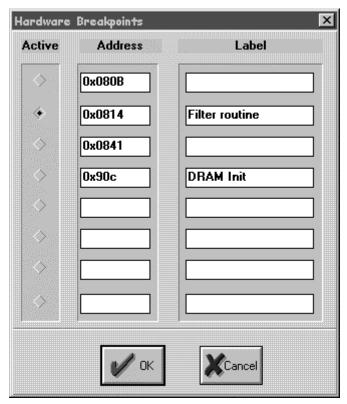

| 5–20 | Hardware Breakpoint Dialog 5-20                             |

| 5–21 | Inspect Dialog                                              |

| 5–22 | Inspect Window                                              |

| 5–23 | I/O Ports Window                                            |

| 5–24 | Debug Menu                                                  |

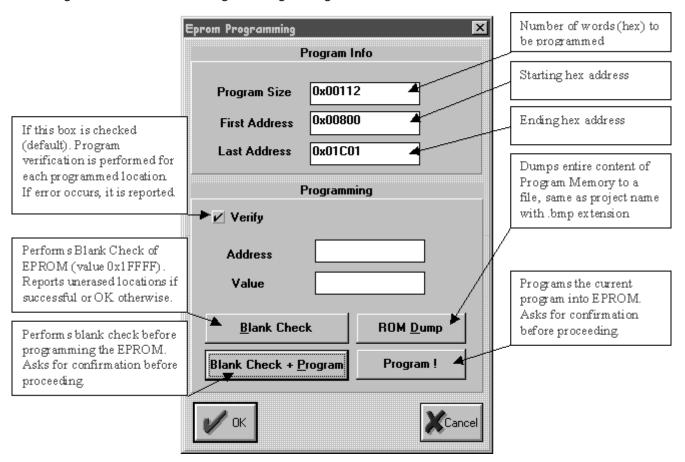

| 5–25 | EPROM Programming Dialog 5-25                               |

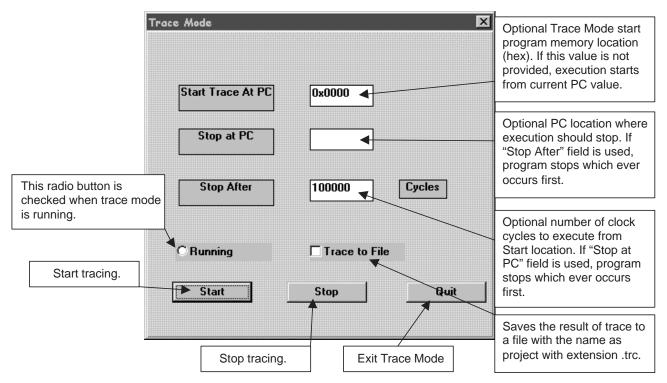

| 5–26 | Trace Mode                                                  |

| 5–27 | Init Menu Option                                            |

| 5–28 | Options Menu                                                |

| 5–29 | Miscellaneous Dialog                                        |

| 5–30 | Windows Menu Options 5-30                                   |

| 5–31 | Context Sensitive Help System                               |

|      |                                                             |

| 7–1  | 100-Pin PJM Mechanical Information 7-4                      |

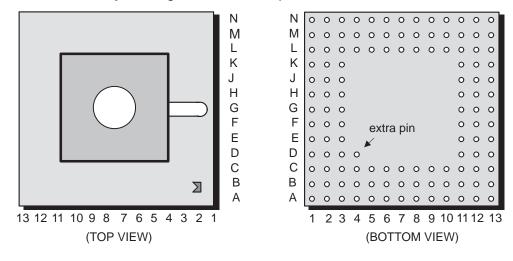

| 7–2  | 120-Pin Grid Array Package for the Development Device, P614 |

| 7–3  | 120 Pin Grid Array (PGA) Package Leads, P614 7-6            |

| 7–4  | Speech Development Cycle 7-8                                |

|      |                                                             |

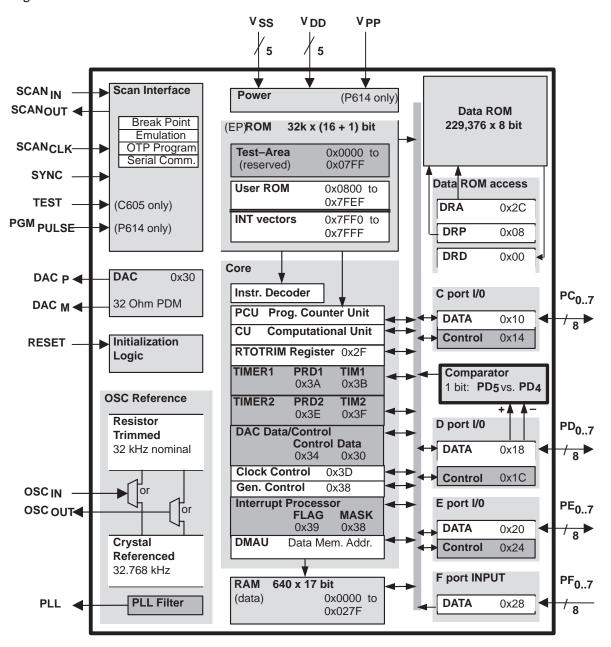

| A–1  | MSP50C605 Architecture                                      |

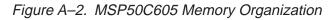

| A–2  | MSP50C605 Memory Organization A-5                           |

| A–3  | MSP50C605 100-Pin PJM Package A-6                           |

| B–1  | MSP50C604 Block Diagram B-4                                 |

| B-2  | MSP50C604 Memory Organization and I/O ports                 |

| B-3  | MSP50C604 Slave Mode Signals                                |

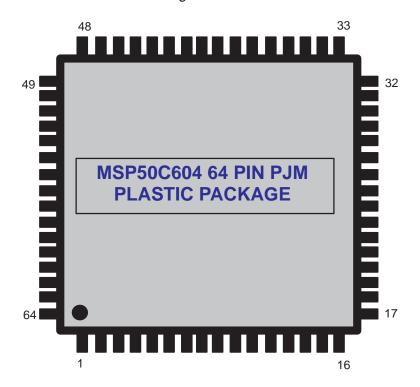

| B-4  | MSP50C604 64-Pin PJM PackageB-9                             |

| 5.   |                                                             |

# **Tables**

| 1–1<br>1–2                                    | Signal and Pad Descriptions for the C614       1-10         MSP50C614 100-Pin PJM Plastic Package Pinout Description       1-11                                                                                                                                                                                                   |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2–1<br>2–2<br>2–3<br>2–4<br>2–5<br>2–6        | Signed and Unsigned Integer Representation2-5Summary of C614's Peripheral Communications Ports2-17Programmable Bits Needed to Control Reduced Power Modes2-37Status of Circuitry When in Reduced Power Modes2-38How to Wake-Up from Reduced Power Modes2-39Destination of Program Counter on Wake-Up Under Various Conditions2-40 |

| 3–1<br>3–2                                    | Interrupts                                                                                                                                                                                                                                                                                                                        |

| 4–1<br>4–2<br>4–3<br>4–4<br>4–5<br>4–6<br>4–7 | Status Register (STAT)4-7Addressing Mode Encoding4-9Rx Bit Description4-10Addressing Mode Bits and {adrs} Field Description4-10MSP50P614/MSP50C614 Addressing Modes Summary4-11Auto Increment and Auto Decrement Modes4-11Flag Addressing Field {flagadrs} for Certain Flag Instructions (Class 8a)4-12                           |

| 4–8<br>4–9<br>4–10                            | Initial Processor State for the Examples Before Execution of Instruction       4-13         Indirect Addressing Syntax       4-15         Symbols and Explanation       4-22                                                                                                                                                      |

| 4–11<br>4–12<br>4–13                          | Instruction Classification       4-23         Classes and Opcode Definition       4-25         Class 1 Instruction Encoding       4-26                                                                                                                                                                                            |

| 4–14<br>4–15<br>4–16                          | Class 1a Instruction Description       4-26         Class 1b Instruction Description       4-27         Class 2 Instruction Encoding       4-29                                                                                                                                                                                   |

| 4–17<br>4–18                                  | Class 2a Instruction Description4-29Class 2b Insstruction Description4-30                                                                                                                                                                                                                                                         |

| 4–19<br>4–20<br>4–21                          | Class 3 Instruction Encoding4-31Class 3 Instsruction Description4-31Class 4a Instruction Encoding4-34                                                                                                                                                                                                                             |

| 4–22<br>4–23<br>4–24                          | Class 4a Instruction Description4-35Class 4b Instruction Description4-35Class 4c Instruction Description4-35                                                                                                                                                                                                                      |

| 4–25 | Class 4d Instruction Description                         | 4-35  |

|------|----------------------------------------------------------|-------|

| 4–26 | Class 5 Instruction Encoding                             | 4-36  |

| 4–27 | Class 5 Instruction Description                          | 4-36  |

| 4–28 | Class 6a Instruction Encoding                            | 4-38  |

| 4–29 | Class 6a Instruction Description                         | 4-38  |

| 4–30 | Class 6b Instruction Description                         | 4-39  |

| 4–31 | Class 7 Instruction Encoding and Description             | 4-40  |

| 4–32 | Class 8a Instruction Encoding                            | 4-41  |

| 4–33 | Class 8a Instruction Description                         | 4-42  |

| 4–34 | Class 8b Instruction Description                         | 4-42  |

| 4–35 | Class 9a Instruction Encoding                            | 4-43  |

| 4–36 | Class 9a Instruction Description                         | 4-43  |

| 4–37 | Class 9b Instruction Description                         | 4-43  |

| 4–38 | Class 9c Instruction Description                         | 4-44  |

| 4–39 | Class 9d Instruction Description                         | 4-44  |

| 4–40 | Data Memory Address and Data Relationship                | 4-46  |

| 4–41 | MSP50P614/MSP50C614 Computational Modes                  | 4-50  |

| 4–42 | Hardware Loops in MSP50P614/MSP50C614                    | 4-54  |

| 4–43 | Initial Processor State for String Instructions          | 4-55  |

| 4–44 | Lookup Instructions                                      |       |

| 4–45 | Auto Increment and Decrement                             | 4-73  |

| 4–46 | Addressing Mode Bits and adrs Field Description          | 4-73  |

| 4–47 | Flag Addressing Syntax and Blts                          | 4-73  |

| 4–48 | Names for cc                                             | 4-87  |

| 5–1  | String Functions                                         | 5-46  |

| 7–1  | MSP50C614 100-Pin PJM Plastic Package Pinout Description | . 7-3 |

| A–1  | MSP50C605 100-Pin PJM Plastic Package Pinout Description | . A-7 |

| B–1  | MSP50C604 64-Pin PJM Plastic Package Pinout Description  | . B-8 |

# Notes, Cautions, and Warnings

| /ISP50C605 and MSP50C604 1-                            | 6 |

|--------------------------------------------------------|---|

| PGA Package                                            | 3 |

| ROM Locations that Hold Interrupt Vectors 2-1          | 8 |

| nstructions with References                            | 9 |

| Block Protection Mode                                  | 1 |

| Block Protections Word                                 | 1 |

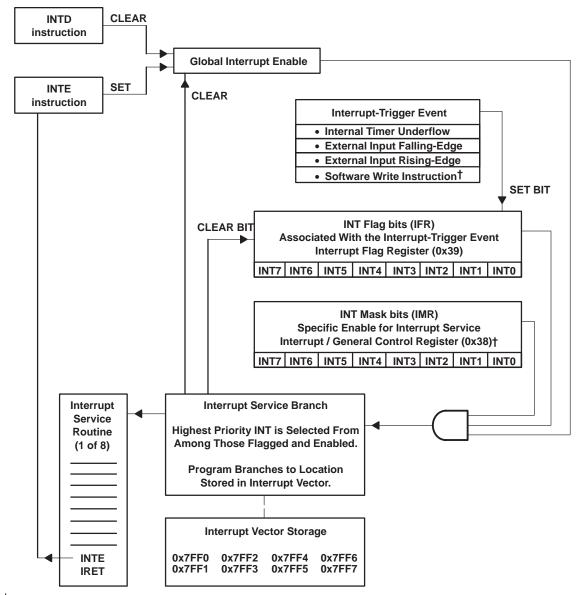

| Setting a Bit in the IFR Using the OUT Instruction     | 4 |

| nterrupt Service Branch                                | 4 |

| Vriting to the TIM Register                            | 7 |

| ClkSpdCtrl Bits 8 and 9 2-3                            | 1 |

| Reference Oscillator Stopped by Programmed Disable 2-3 | 2 |

| Register Trim Value                                    | 3 |

| dle State Clock Control Bit 2-3                        | 6 |

| Reading the Data Register                              | 2 |

| PDM Enable Bit                                         | 9 |

| ntGenCtrl Register Bit 15 3-1                          | 6 |

| nternal RAM State after Reset 3-2                      | 0 |

| Stack Pointer Initialization                           | 1 |

| Data Memory Access                                     | 5 |

| Scan Port Bond Out                                     | 2 |

| /ISP50C605                                             | 1 |

| MSP50C604 B-                                           | 1 |

## **Chapter 1**

## Introduction to the MSP50C614

The MSP50C614 (C614) is a low cost, mixed signal controller, that combines a speech synthesizer, general-purpose I/O, onboard ROM, and direct speaker-drive in a single package. The computational unit utilizes a powerful new DSP which gives the C614 unprecedented speed and computational flexibility compared with previous devices of its type. The C614 supports a variety of speech and audio coding algorithms, providing a range of options with respect to speech duration and sound quality.

| Topio | c                                            | Page |

|-------|----------------------------------------------|------|

| 1.1   | Features of the C614                         | 1–2  |

| 1.2   | Applications                                 | 1–3  |

| 1.3   | Development Version: P614                    | 1–4  |

| 1.4   | Functional Description                       | 1–5  |

| 1.5   | C605 and C604                                | 1–6  |

| 1.6   | Terminal Assignments and Signal Descriptions | 1–10 |

## 1.1 Features of the C614

- Advanced, integrated speech synthesizer for high quality sound

- Operates up to 8 MHz (performs up to 8 MIPS)

- U Very low-power operation, ideal for hand-held devices

- Low voltage operation, sustainable by three batteries

- Reduced power stand-by modes, less than 10 μA in deep-sleep mode

- Supports high-quality synthesis algorithms such as MELP, CELP, LPC, and ADPCM

- Contains 32K words onboard ROM (2K words reserved)

- 640 words RAM

- □ 40 general purpose, bit configurable I/O

- 8 inputs with programmable pullup resistors and a dedicated interrupt (key-scan)

- 16 dedicated output pins

- $\Box$  Direct speaker driver, 32  $\Omega$  (PDM)

- One-bit comparator with edge-detection interrupt service (IMPORTANT: Not currently supported)

- Resistor-trimmed oscillator or 32-kHz crystal reference oscillator

- Serial scan port for in-circuit emulation and diagnostics

- The MSP50C614 is sold in die form; an emulator device for the MSP50C614 is sold in a ceramic package for development.

## 1.2 Applications

Due to its low cost, low-power needs, and high programmability, the C614 is suitable for a wide variety of applications incorporating I/O control and high-quality speech:

| Talking To | ys 🗋 | Talking Books |

|------------|------|---------------|

|------------|------|---------------|

- Electronic Learning Aids

Talking Dictionaries

- Games

Warning Systems

- Talking Clocks

Equipment for the Handicapped

## 1.3 Development Device: MSP50P614

The MSP50P614 is an EPROM based version of the MSP50C614, and is available in 120 pin windowed ceramic pin grid array. This EPROM based version of the device is only available in limited quantities to support software development. Since the MSP50P614 program memory is EPROM, each person doing software development should have several of these PGA packaged devices.

The MSP software development tool supports non-real-time debugging by scanning the code sequence through the MSP50C614/MSP50P614 scanport without programming the EPROM. However, the rate of code execution is limited by the speed of the PC parallel port. Any MSP50C614/MSP50P614 can be used in this debugging mode.

The MSP50P614 EPROM must be programmed to debug the code in real time. The MSP software development tool is used to program the EPROM, set a breakpoint, and evaluate the internal registers after the breakpoint is reached. If a change is made to the code, the code will need to be updated and programmed into another device while erasing previous devices. This cycle of programming, debugging, and erasing typically requires 10–15 devices to be in the eraser at any one time, so 15–20 devices may be required to operate efficiently. The windowed PGA version of the MSP50P614 is required for this debugging mode.

## **1.4 Functional Description**

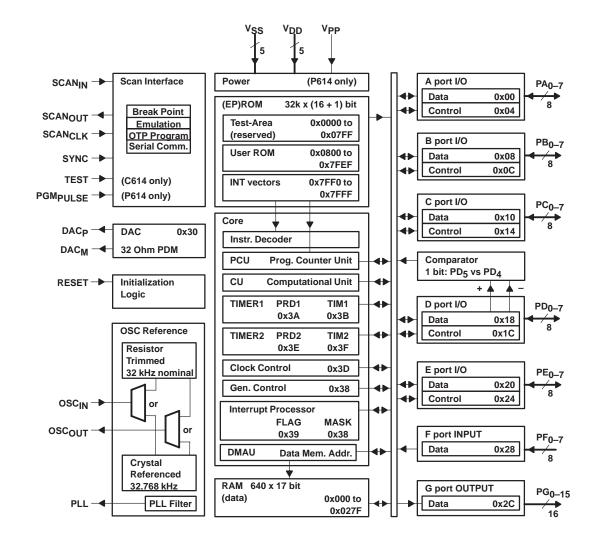

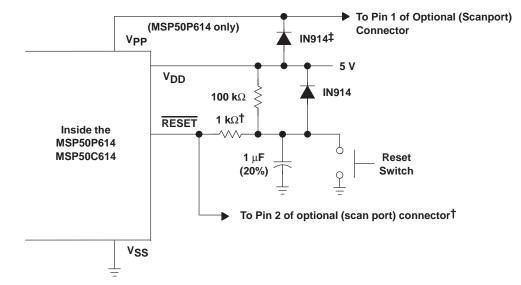

The device consists of a micro-DSP core, embedded program and data memory, and a self-contained clock generation system. General-purpose periphery is comprised of 64 bits of partially configurable I/O.

The core processor is a general-purpose 16 bit micro-controller with DSP capability. The basic core block includes a computational unit (CU), data address unit, program address unit, two timers, eight level interrupt processor, and several system and control registers. The core processor gives the P614 and C614 break-point capability in emulation.

The processor is a Harvard type for efficient DSP algorithm execution. It requires separate program and data memory blocks to permit simultaneous access. The ROM has a protection scheme to prevent third-party pirating. It is configured in 32K 17-bit words.

The total ROM space is divided into two areas: 1) The lower 2K words are reserved by Texas Instruments for a built-in self-test, 2) the upper 30K is for user program/data.

The data memory is internal static RAM. The RAM is configured in 640 17-bit words. Both memories are designed to consume minimum power at a given system clock and algorithm acquisition frequency.

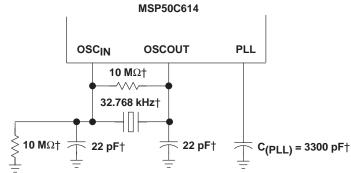

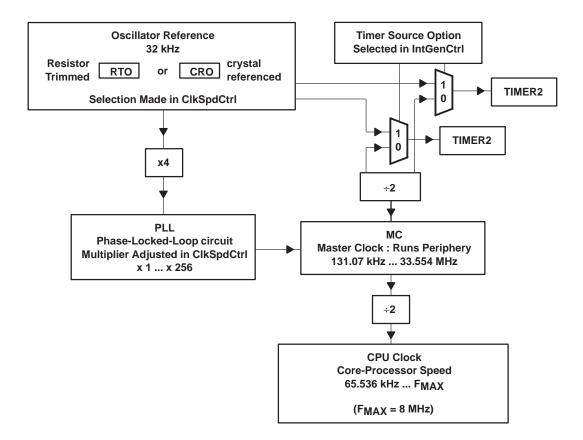

A flexible clock generation system is included that enables the software to control the clock over a wide frequency range. The implementation uses a phase-locked loop (PLL) circuit that drives the processor clock at a selectable frequency between the minimum and maximum achievable. Selectable frequencies for the processor clock are spaced apart in 65.536-kHz steps. The PLL clock-reference is also selectable; either a resistor-trimmed oscillator or a crystal-referenced oscillator may be used. Internal and peripheral clock sources are controlled separately to provide different levels of power management (see Figure 1–2).

The peripheral consists of five 8-bit wide general-purpose I/O ports, one 8-bit wide dedicated input port, and one 16-bit wide dedicated output port. The bidirectional I/O can be configured under software control as either high-impedance inputs or as totem-pole outputs. They are controlled via addressable I/O registers. The input-only port has a programmable pullup option (100-k $\Omega$  minimum resistance) and a dedicated service interrupt. These features make the input port especially useful as a key-scan interface.

A simple one-bit comparator is also included in the periphery. The comparator is enabled by a control register, and its pin access is shared with two pins in one of the general-purpose I/O ports. Rounding out the C614 periphery is a

built in pulse-density-modulated DAC (digital-to-analog converter) with direct speaker-drive capability. The block diagram appearing in Figure 1–1 gives an overview of the C614 functionality. IMPORTANT: a one bit comparator is not currently supported.

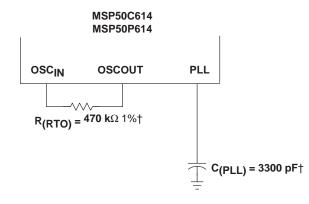

Typical connections to implement reset functionality are shown in Figure 1–3.

## 1.5 C605 and C604 (Preliminary Information)

Two related products, the MSP50C605 (C605) and MSP50C604(C604) use the C614 core. The C605 has a 224K byte data ROM built into the chip and 32 I/O port pins. The C605 can provide up to 30 minutes of uninterrupted speech. The C604 is designed to support slave operation with an external host microcontroller. In this mode the C604 can be programmed with a code that communicates with the host via a command set. This command set can be designed to support LPC, CELP, MELP, and ADPCM coders by selecting the appropriate command. The C604 can also be used stand-alone in master mode. The C604 and the C605 use the P614 as the development version device. Details on C605 and C604 processors are found in Appendix A and B.

### Note: MSP50C605 and MSP50C604

MSP50C605 and MSP50C604 are in the Product Preview stage of development. For more information contact your local TI sales office. See Appendices A and B for more information.

Figure 1–1. Functional Block Diagram for the C614

Introduction to the MSP50C614 1-7

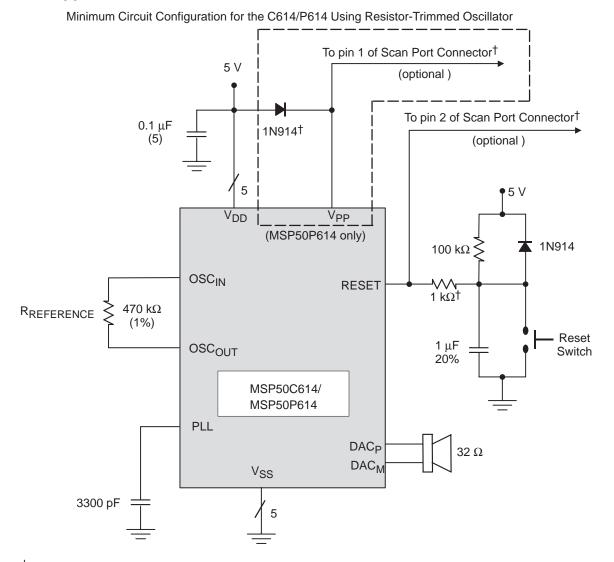

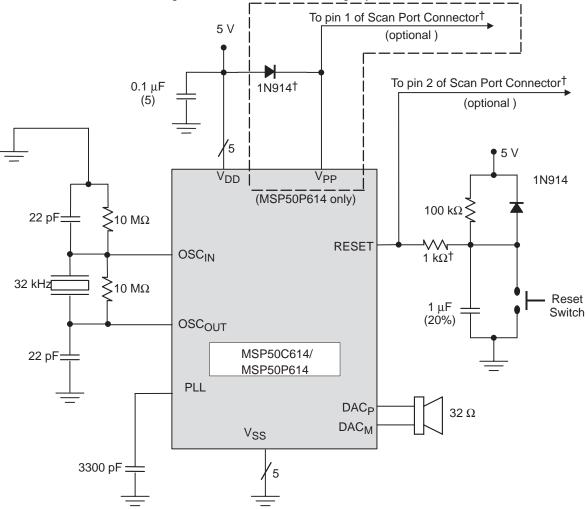

Figure 1–2. Oscillator and PLL Connection

a) Crystal Oscillator Operation Connections

$^{\dagger}$  Keep these components as close as possible to the OSC\_IN, OSC\_OUT, and PLL pins.

b) Resistor Trim Operation Connections

$^{\dagger}$  Keep these components as close as possible to the OSC\_{IN}, OSC\_{OUT}, and PLL pins.

Figure 1–3. RESET Circuit

<sup>†</sup> If it is necessary to use the software development tools to control the MSP50P614 in application board, the 1 k $\Omega$  resistor is needed to allow the development tool to over drive the RESET circuit on the application board.

<sup>‡</sup> This Diode can be omitted (shorted) if the application does not require use of the scanport interface. See Section 7.1.1 regarding scan port bond out.

## 1.6 Terminal Assignments and Signal Descriptions

| SIGNAL                             | PAD NUMBER          | I/O            | DESCRIPTIO                        | DESCRIPTION |  |  |

|------------------------------------|---------------------|----------------|-----------------------------------|-------------|--|--|

|                                    | Inj                 | out/Output Por | ts                                |             |  |  |

| PA <sub>0</sub> – PA <sub>7</sub>  | 75  ightarrow 68    | I/O            | Port A general-purpose I/O        | (1 Byte)    |  |  |

| PB <sub>0</sub> – PB <sub>7</sub>  | 85  ightarrow 78    | I/O            | Port <b>B</b> general-purpose I/O | (1 Byte)    |  |  |

| PC <sub>0</sub> – PC <sub>7</sub>  | $8 \rightarrow 1$   | I/O            | Port C general-purpose I/O        | (1 Byte)    |  |  |

| PD <sub>0</sub> – PD <sub>7</sub>  | $18 \rightarrow 11$ | I/O            | Port <b>D</b> general-purpose I/O | (1 Byte)    |  |  |

| PE <sub>0</sub> – PE <sub>7</sub>  | 63  ightarrow 56    | I/O            | Port E general-purpose I/O        | (1 Byte)    |  |  |

| PF <sub>0</sub> – PF <sub>7</sub>  | $31 \rightarrow 24$ | I              | Port F key-scan input             | (1 Byte)    |  |  |

| PG <sub>0</sub> – PG <sub>7</sub>  | $49 \to 42$         | 0              | Port G dedicated output           | (2 Bytes)   |  |  |

| PG <sub>8</sub> – PG <sub>15</sub> | $39 \rightarrow 32$ |                |                                   |             |  |  |

Table 1–1. Signal and Pad Descriptions for the C614

Pins **PD4** and **PD5** may be dedicated to the comparator function, if the comparator enable bit is set. Refer to Section 3.3, *Comparator*, for details. (Currently not supported)

| Scan Port Control Signals |    |   |                                               |  |  |

|---------------------------|----|---|-----------------------------------------------|--|--|

| SCANIN                    | 54 | I | Scan port data input                          |  |  |

| SCANOUT                   | 50 | 0 | Scan port data output                         |  |  |

| SCANCLK                   | 53 | I | Scan port clock                               |  |  |

| SYNC                      | 52 | I | Scan port synchronization                     |  |  |

| TEST<br>PGMPULSE          | 51 | I | C614 : test modes<br>P614 : programming pulse |  |  |

The scan port pins must be bonded out on any C614 production board. Consult the "Important Note regarding Scan Port Bond Out", Section 7.1.1, *Scan Port Bond Out*.

| Oscillator Reference Signals |                                 |                                     |                                |  |  |  |  |

|------------------------------|---------------------------------|-------------------------------------|--------------------------------|--|--|--|--|

| OSCIN                        | 65                              | I                                   | Resistor/crystal reference in  |  |  |  |  |

| OSCOUT                       | 66                              | O Resistor/crystal reference out    |                                |  |  |  |  |

| PLL                          | 67                              | 0                                   | Phase-lock-loop filter         |  |  |  |  |

| DAC Sound Output             |                                 |                                     |                                |  |  |  |  |

| DACP                         | 22                              | 0                                   | Digital-to-analog output 1 (+) |  |  |  |  |

| DACM                         | 20                              | 20 O Digital-to-analog output 2 (–) |                                |  |  |  |  |

|                              | In                              | itialization                        |                                |  |  |  |  |

| RESET                        | 55                              | I                                   | Initialization                 |  |  |  |  |

| Power Signals                |                                 |                                     |                                |  |  |  |  |

| V <sub>SS</sub>              | 9, 19 <sup>†</sup> , 40, 64, 76 |                                     | Ground                         |  |  |  |  |

| V <sub>DD</sub>              | 10, 21†, 23, 41, 77             |                                     | Processor power (+)            |  |  |  |  |

<sup>†</sup> Pads V<sub>SS</sub> (19) and V<sub>DD</sub> (21) service the DAC circuitry. Their pins tend to sustain a higher current draw. A dedicated decoupling capacitor across these pins is therefore required. Refer to Section 6.1, *Application Circuits*, for details.

The C614 is sold in die form for its volume production. Contact you local TI sales office for mount and bond information.

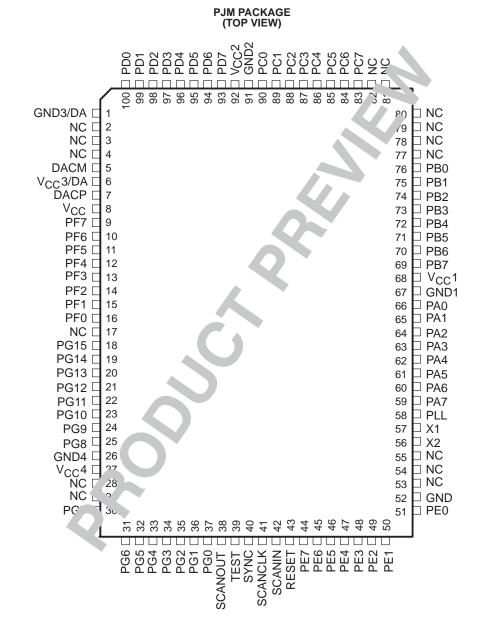

MSP50C614 is also available in 100 pin plastic QFP package. The pinout is shown in Figure 1–4 and Table 1–2.

| Description          | Pin # | Description       | Pin # | Description       | Pin # | Description       | Pin # |

|----------------------|-------|-------------------|-------|-------------------|-------|-------------------|-------|

| GND3/DA              | 1     | GND4              | 26    | PE <sub>0</sub>   | 51    | PB <sub>0</sub>   | 76    |

| NC                   | 2     | V <sub>CC</sub> 4 | 27    | GND               | 52    | NC                | 77    |

| NC                   | 3     | NC                | 28    | NC                | 53    | NC                | 78    |

| NC                   | 4     | NC                | 29    | NC                | 54    | NC                | 79    |

| DAC <sub>M</sub>     | 5     | PG <sub>7</sub>   | 30    | NC                | 55    | NC                | 80    |

| V <sub>CC</sub> 3/DA | 6     | PF <sub>6</sub>   | 31    | X2                | 56    | NC                | 81    |

| DACP                 | 7     | PF <sub>5</sub>   | 32    | X1                | 57    | NC                | 82    |

| V <sub>CC</sub>      | 8     | PF <sub>4</sub>   | 33    | PLL               | 58    | PC <sub>7</sub>   | 83    |

| PF <sub>7</sub>      | 9     | PF <sub>3</sub>   | 34    | PA <sub>7</sub>   | 59    | PC <sub>6</sub>   | 84    |

| PF <sub>6</sub>      | 10    | PF <sub>2</sub>   | 35    | PA <sub>6</sub>   | 60    | PC <sub>5</sub>   | 85    |

| PF <sub>5</sub>      | 11    | PF <sub>1</sub>   | 36    | PA <sub>5</sub>   | 61    | PC <sub>4</sub>   | 86    |

| PF <sub>4</sub>      | 12    | PF <sub>0</sub>   | 37    | PA <sub>4</sub>   | 62    | PC <sub>3</sub>   | 87    |

| PF <sub>3</sub>      | 13    | SCANOUT           | 38    | PA3               | 63    | PC <sub>2</sub>   | 88    |

| PF <sub>2</sub>      | 14    | TEST              | 39    | PA <sub>2</sub>   | 64    | PC <sub>1</sub>   | 89    |

| PF <sub>1</sub>      | 15    | SYNC              | 40    | PA <sub>1</sub>   | 65    | PC <sub>0</sub>   | 90    |

| PF <sub>0</sub>      | 16    | SCANCLK           | 41    | PA <sub>0</sub>   | 66    | GND2              | 91    |

| NC                   | 17    | SCANIN            | 42    | GND1              | 67    | V <sub>CC</sub> 2 | 92    |

| PG <sub>15</sub>     | 18    | RESET             | 43    | V <sub>CC</sub> 1 | 68    | PD <sub>7</sub>   | 93    |

| PG <sub>14</sub>     | 19    | PE7               | 44    | PB <sub>7</sub>   | 69    | PD <sub>6</sub>   | 94    |

| PG <sub>13</sub>     | 20    | PE <sub>6</sub>   | 45    | PB <sub>6</sub>   | 70    | PD <sub>5</sub>   | 95    |

| PG <sub>12</sub>     | 21    | PE5               | 46    | PB <sub>5</sub>   | 71    | PD <sub>7</sub>   | 96    |

| PG <sub>11</sub>     | 22    | PE <sub>4</sub>   | 47    | PB <sub>4</sub>   | 72    | PD <sub>73</sub>  | 97    |

| PG <sub>10</sub>     | 23    | PE3               | 48    | PB3               | 73    | PD <sub>2</sub>   | 98    |

| PG <sub>9</sub>      | 24    | PE <sub>2</sub>   | 49    | PB <sub>2</sub>   | 74    | PD <sub>1</sub>   | 99    |

| PG <sub>8</sub>      | 25    | PE <sub>1</sub>   | 50    | PB <sub>1</sub>   | 75    | PD <sub>0</sub>   | 100   |

Table 1–2. MSP50C614 100-Pin PJM Plastic Package Pinout Description

Introduction to the MSP50C614 1-11

Figure 1–4. MSP50C614 100 Pin PJM PLastic Package Pinout (Preliminary Information)

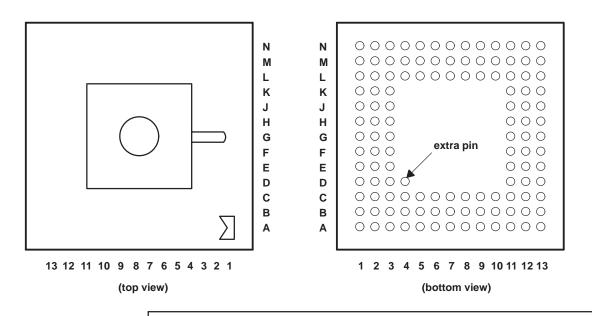

For software development and prototyping, a windowed ceramic 120-pin grid array packaged P614 is available. The P614's PGA package is shown in Figure 1–5 and Table 1–3:

Figure 1–5. 120 Pin Grid Array Package for the Development Device, P614

MSP50P614

#### Note: PGA Package

The PGA package is only available in limited quantities for development purposes.

The pin assignments for the 120-pin PGA package (P614 device only) are outlined in the following table. Refer to Section 1.6 for more information on the signal functions.

| Ν | nc              | nc              | V <sub>DD</sub> † | PF7                          | $PF_5$          | PF <sub>2</sub> | V <sub>PP</sub> | PG <sub>15</sub> | PG <sub>12</sub> | PG <sub>10</sub> | V <sub>SS</sub>   | V <sub>DD</sub>                 | nc  |  |  |

|---|-----------------|-----------------|-------------------|------------------------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|-------------------|---------------------------------|-----|--|--|

| Μ | nc              | nc              | DACM              | DACP                         | PF <sub>6</sub> | PF3             | PF <sub>1</sub> | PG <sub>14</sub> | PG <sub>11</sub> | PG8              | nc                | nc                              | PG7 |  |  |

| L | PD <sub>0</sub> | nc              | nc                | Vss†                         | V <sub>DD</sub> | PF <sub>4</sub> | PF <sub>0</sub> | PG <sub>13</sub> | PGg              | nc               | nc                | PG5                             | PG4 |  |  |

| Κ | PD3             | PD <sub>1</sub> | nc                |                              |                 |                 | PG <sub>6</sub> | PG3              | PG <sub>1</sub>  |                  |                   |                                 |     |  |  |

| J | $PD_5$          | PD <sub>4</sub> | PD <sub>2</sub>   |                              |                 |                 |                 |                  |                  |                  |                   | PG <sub>2</sub> PG <sub>0</sub> |     |  |  |

| Н | V <sub>DD</sub> | PD7             | PD <sub>6</sub>   |                              |                 |                 |                 |                  |                  |                  |                   | q                               |     |  |  |

| G | V <sub>SS</sub> | PC <sub>1</sub> | PC <sub>0</sub>   | (bottom view) RESET scanin P |                 |                 |                 |                  | (bottom view)    |                  |                   |                                 |     |  |  |

| F | PC <sub>2</sub> | PC <sub>3</sub> | PC <sub>4</sub>   |                              |                 |                 |                 |                  |                  |                  |                   | PE5                             | PE6 |  |  |

| Е | PC5             | PC <sub>6</sub> | nc                |                              |                 |                 |                 |                  |                  |                  |                   | PE2                             | PE3 |  |  |

| D | PC7             | nc              | nc                | extra                        |                 |                 |                 |                  |                  |                  | nc                | VSS                             | PE1 |  |  |

| С | nc              | nc              | nc                | nc                           | PB <sub>1</sub> | PB5             | VSS             | PA3              | PA7              | nc               | nc                | nc                              | nc  |  |  |

| В | nc              | nc              | nc                | PB0                          | PB3             | PB <sub>6</sub> | PA <sub>0</sub> | PA <sub>2</sub>  | PA5              | PLL              | OSCOUT            | nc                              | nc  |  |  |

| Α | nc              | nc              | nc                | PB <sub>2</sub>              | PB4             | PB7             | V <sub>DD</sub> | PA <sub>1</sub>  | PA4              | PA <sub>6</sub>  | OSC <sub>IN</sub> | nc                              | nc  |  |  |

|   | 1               | 2               | 3                 | 4                            | 5               | 6               | 7               | 8                | 9                | 10               | 11                | 12                              | 13  |  |  |

<sup>†</sup> It is important to provide a separate decoupling capacitor for the V<sub>DD</sub>, V<sub>SS</sub> pair which services the DAC. These pins are PGA numbers N3 and L4, respectively. The relatively high current demands of the digital-to-analog circuitry make this a requirement. Refer to Section 6.1, *TBD*, for details.

## Chapter 2

# MSP50C614 Architecture

A detailed description of MSP50C614 architecture is included in this chapter. After reading this chapter, the reader will have in-depth knowledge of internal blocks, memory organization, interrupt system, timers, clock control mechanism, and various low power modes.

## Topic

## Page

| 2.1  | Architecture Overview                 |

|------|---------------------------------------|

| 2.2  | Computation Unit                      |

| 2.3  | Data Memory Address Unit              |

| 2.4  | Program Counter Unit 2–14             |

| 2.5  | Bit Logic Unit                        |

| 2.6  | Memory Organization: RAM and ROM 2–15 |

| 2.7  | Interrupt Logic 2-22                  |

| 2.8  | Timer Registers 2–26                  |

| 2.9  | Clock Control                         |

| 2.10 | Execution Timing 2–33                 |

| 2.11 | Reduced Power Modes         2–34      |

|      |                                       |

## 2.1 Architecture Overview

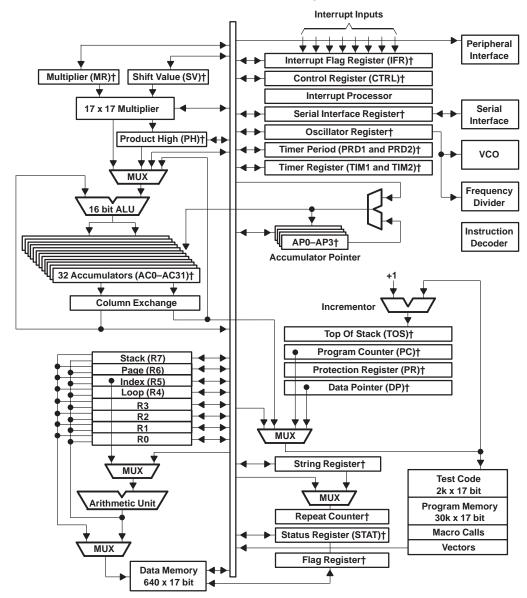

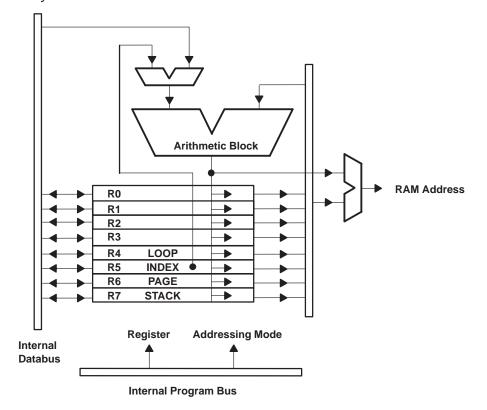

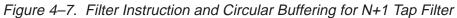

The core processor in the C614 is a medium performance mixed signal processor with enhanced microcontroller features and a limited DSP instruction set. In addition to its basic multiply/accumulate structure for DSP routines, the core provides for a very efficient handling of string and bit manipulation. A unique accumulator-register file provides additional scratch pad memory and minimizes memory thrashing for many operations. Five different addressing modes and many short direct references provide enhanced execution and code efficiency.

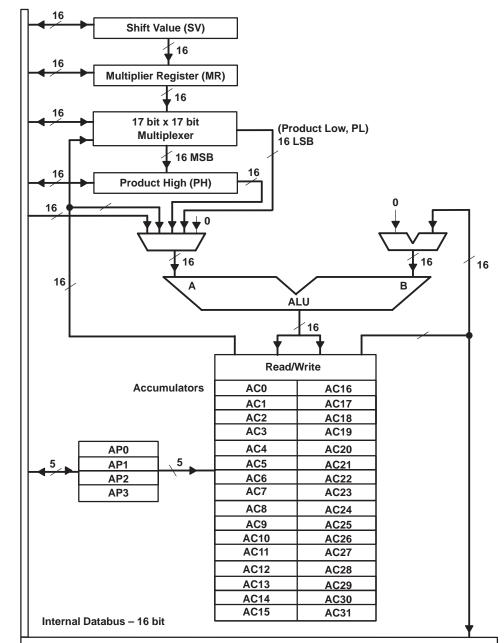

The basic elements of the C614 core are shown in Figure 2–1. In addition to the main computational units, the core's auxiliary functions include two timers, an eight-level interrupt processor, a clock generation circuit, a serial scan-port interface, and a general control register.

<sup>†</sup> Indicates internal programmable registers.

Figure 2–2. Computational Unit Block Diagram (The shaded boxes represent internal programmable registers.)

## 2.2 Computation Unit

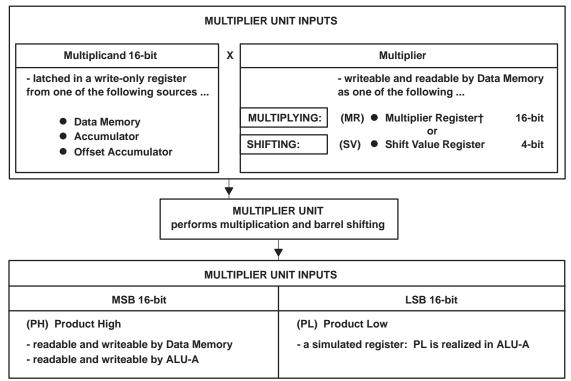

The computational unit (CU) is comprised of a (17-bit by 17-bit) Booth's algorithm multiplier and a 16-bit arithmetic logic unit (ALU). The block diagram of the CU is shown in Figure 2–2. The multiplier block is served by 4 system registers: a 16-bit multiplier register (MR), a 16-bit write-only multiplicand register, a 16-bit high word product register (PH), and a 4-bit shift value register (SV). The output of the ALU is stored in one 16-bit accumulator from among the 32 which compose the accumulator-register block. The accumulator register block can supply either one operand to the ALU (addressed accumulator register or its offset register) or two operands to the ALU (both the addressed register and its offset).

### 2.2.1 Multiplier

The multiplier executes a 17-bit by 17-bit 2s complement multiply and multiply-accumulate in a single instruction cycle. The sign bit within each operand is bit 16, and its value extends from bit 0 (LSB) to bit 15 (MSB). The sign bit for either operand (multiplier or multiplicand) can assume a positive value (zero) or a value equal to the MSB (bit 15). In assuming zero, the extra bit supports unsigned multiplication. In assuming the value of bit 15, the extra bit supports signed multiplication. Table 2–1 shows the greater magnitude achievable when using unsigned multiplication (65535 as opposed to 32767).

| Table 2–1. | Signed and | Unsigned | Integer | Representation |

|------------|------------|----------|---------|----------------|

|            |            |          |         |                |

| Un      | signed | Signed  |        |  |

|---------|--------|---------|--------|--|

| Decimal | Hex    | Decimal | Hex    |  |

| 65535   | 0xFFFF | -1      | 0xFFFF |  |

| 32768   | 0x8000 | -32768  | 0x8000 |  |

| 32767   | 0x7FFF | 32767   | 0x7FFF |  |

| 0       | 0x0000 | 0       | 0x0000 |  |

During multiplication, the lower word (LSB) of the resulting product, product low, is multiplexed to the ALU. Product low is either loaded to or arithmetically combined with an accumulator register. These steps are performed within the same instruction cycle. Refer to Figure 2–3. At the end of the current execution cycle, the upper word (MSB) of the product is latched into the product high register (PH). The multiplicand source can be either data memory, an accumulator, or an accumulator offset. The multiplier source can be either the 16-bit multiplier register (MR) or the 4-bit shift value (SV) register. For all multiply operations, the MR register stores the multiplier operand. For barrel shift instructions, the multiplier operand is a 4-to-16-bit value that is decoded from the 4-bit shift value register (SV). Refer to Figure 2–4.

As an example of a barrel shift operation, a coded value of 0x7 in the SV register results in a multiplier operand of 0000000010000000 (1 at bit 7). This causes a left-shift 7-times on the 16 bit multiplicand. The output result is 32-bit. On the other hand, if the status bit FM (multiplier shift mode) is SET, then the multiplier operand (000000010000000) is left-shifted once to form a 17 significant-bit operand (000000010000000). This mode is included to avoid a divide-by-2 of the product, when interpreting the input operands as signed binary fractions. The multiplier shift mode status bit is located in the status register (STAT).

All three multiplier registers (PH, SV, and MR) can be loaded from data memory and stored to data memory. In addition, data can be transferred from an accumulator register to the PH, or vice versa. Both long and short constants can be directly loaded to the MR from program memory.

The multiplicand is latched in a write-only register from the internal data bus. The value is not accessible by memory or other system registers.

Figure 2–3. Overview of the Multiplier Unit Operation

<sup>†</sup> Also write-able by Program Memory

# 2.2.2 Arithmetic Logic Unit

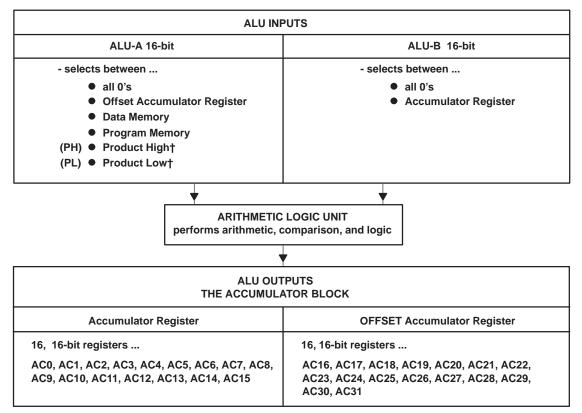

The arithmetic logic unit is the focal point of the computational unit, where data can be added, subtracted, and compared. Logical operations can also be performed by the ALU. The basic hardware word-length of the ALU is 16 bits; however, most ALU instructions can also operate on strings of 16-bit words (i.e., a series or array of values). The ALU operates in conjunction with a flexible, 16-bit accumulator register block. The accumulator register block is composed of 32, 16-bit registers which further enhances execution and promotes compact code.

The ALU has two distinct input paths, denoted ALU-A and ALU-B (see Figure-2–4). The ALU-A input selects between all zeros, the internal databus, the product high register (PH), the product low (PL), or the offset output of the accumulator register block. The ALU-B input selects between all zeros and the output from the accumulator register block.

The all-zero values are necessary for data transfers and unitary operations. All-zeros also serve as default values for the registers, which helps to minimize residual power consumption. The databus path through ALU-A is used to input memory values (RAM) and constant values (program memory) to the ALU. The PH and PL inputs are useful for supporting multiply-accumulate operations (refer to Section 2.2.1, *Multiplier*).

The operations supported by the ALU include arithmetic, logic, and comparison. The arithmetic operations are addition, subtraction, and load (add to zero). The logical operations are AND, OR, XOR, and NOT. Comparison includes equal-to and not-equal-to. The compare operations may be used with constant, memory, or string values without destroying any accumulator values.

#### 2.2.2.1 Accumulator Block

The output of the ALU is the accumulator block. The accumulator block is composed of 32, 16-bit registers. These registers are organized into two terminals, denoted accumulator and OFFSET accumulator. The terminals provide references for all of the data which is to be held in the accumulator block. The accumulator incorporates one-half of the 32 accumulator registers: AC0..AC15. The OFFSET accumulator incorporates the other half: AC16..AC31.

Figure 2–4. Overview of the Arithmetic Logic Unit

<sup>†</sup> For multiply-accumulate operations.

#### 2.2.2.2 Accumulator Pointer Block

There are four 5-bit registers which are used to store pointers to members of the accumulator block. The accumulator pointers (AP0, AP1, AP2, AP3) are used in two modes: 1) as a direct reference to one of 32, or 2) as an indirect reference. The indirect reference includes a direct reference to one of 16 and an offset (optional) which increments the reference by 16: AC(N+16). For example, AC0 has its offset register located at AC16. AC1 has an offset register located at AC16. AC1 has an offset register located at AC17, and so on. The block is circular: address 31, when incremented, results in address 0. The offsets of AC16 through AC31, therefore, are AC0 through AC15, respectively. See Figure 2–5 Indirect referencing by the AP pointers is supported by most of the C614's accumulator-referenced instructions.

When writing an accumulator-referenced instruction, therefore, the working accumulator address is stored in one of AP0 to AP3. The C614 instruction set provides a two-bit field for all accumulator referenced instructions. The two-bit field serves as a reference to the accumulator pointer which, in turn, stores the address of the actual 16-bit accumulator. Some MOV instructions store the contents of the APn directly to memory or load from memory to the APn register. Other instructions can add or load 5-bit constants to the current APn register contents. A full description of the C614 instruction set is given in Chapter 4, *Instructions*.

#### Figure 2–5. Overview of the Arithmetic Logic Unit

| Accumulato | r Block:                                                      | 32, 16-bit registers    | AC(0          | )) AC(31)                      |

|------------|---------------------------------------------------------------|-------------------------|---------------|--------------------------------|

| Accumulato | r Block Pointers:                                             | 4, 5-bit registers      | AP(0          | )) AP(3)                       |

|            | The accumulator block pointers                                | may assume values in    | n one of two  | forms:                         |

|            | 1) DIRECT REFERENCE:                                          | 0 31                    |               |                                |

|            |                                                               |                         |               | AC Register #                  |

|            | 2) INDIRECT REFERENCE:                                        | 0 15                    | points to:    | 0 15                           |

|            |                                                               | 015 OFFSET              | points to:    | 16 31                          |

|            |                                                               | 1531 OFFSET             | points to:    | 0 15                           |

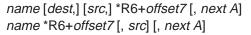

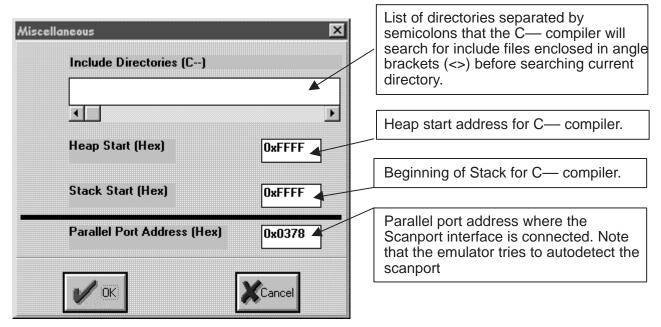

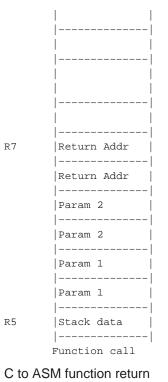

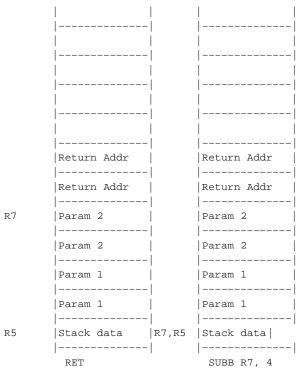

|            | - AP registers are served by a 5-b                            | oit processor for seque | ncing addres  | sses or repetitive operations. |